Irrational Analysis is heavily invested in the semiconductor industry.

Please check the ‘about’ page for a list of active positions.

Positions will change over time and are regularly updated.

Opinions are authors own and do not represent past, present, and/or future employers.

All content published on this newsletter is based on public information and independent research conducted since 2011.

This newsletter is not financial advice, and readers should always do their own research before investing in any security.

Feel free to contact me via email at: irrational_analysis@proton.me

Welcome to a profile on DreamBig Semiconductor.

One of their investors set up couple meetings with me and Sohail, the CEO. Tech is so cool that I asked them if I could write up a summary so here we are.

Additional Disclosures:

I hold no economic interest in DreamBig Semi or any venture capital fund.

Nobody has paid me to write this post.

The investor who put me in touch with DreamBig has reviewed this post before publishing to make sure there are no NDA violations.

Main concern is accidental leaks of DreamBig partner confidential information.

No editorial changes were made.

Who are DreamBig?

DreamBig consists of the old Marvell leadership power couple and a variety of networking pros. A large portion of the former Intel Mount Evans team works at DreamBig now.

A lot of emphasis was placed upon this team’s ability to execute on an ultra-high capacity RDMA engine. In short, this digital IP block handles huge amounts of packets for [R]emote [M]emory [D]irect [A]ccess.

RDMA exists to bypass the CPU and many layers of the traditional networking stack.

Very important for modern AI workloads.

DreamBig claims that they are the only company with a high-quality RMDA IP, excluding Nvidia. They even beat Nvidia in packet processing.

Millions of packets per second (Mpps) is the key metric. Of course, it matters how large the packets are. DreamBig has repeatedly claimed they crush Nvidia in this metric and they have the numbers to back this up. Conversely, Nvidia has stopped publishing Mpps benchmark numbers for ConnectX.

https://dreambigsemi.com/report/

https://dreambigsemi.com/wp-content/uploads/2025/01/RDMA-Performance-Report.pdf

https://dreambigsemi.com/wp-content/uploads/2025/01/RDMA-Validation-Report.pdf

The Chiplet Hub

DreamBig sort of embraced their name and made a crazy super chiplet hub.

This thing is surrounded by UCIe PHYs and has 3D-stacked HBM to act as a cache.

The Demios Chiplet hub enables really cool, ultra-scalable topologies.

They can chain these chiplet hubs to make bigger NICs or complex, heterogeneous AI topologies. AI ASIC chiplets, CPU chiplets, more Ares (DreamBig 800G RDMA engine) chiplets, … whatever.

Super NIC

Normally, the RDMA engine of a NIC is limited by the packet buffer. DreamBig (via the Demios chiplet hub) can massively scale up their packet buffer using the 3D-stacked HBM.

Nvidia does not have this scaling vector. DreamBig appears to have real performance and (more importantly) cost advantages over Nvidia ConnectX 8.

They Have Real Traction

It’s all well and good to make performance claims in simulators and say that your solution can scale in slides. In reality, lots of things can go wrong, especially with something crazy like this chiplet hub.

3D-stacked HBM might have thermal issues.

Packing so many UCIe PHYs together may lead to crosstalk issues.

The RDMA and NoC digital IPs may have timing bugs.

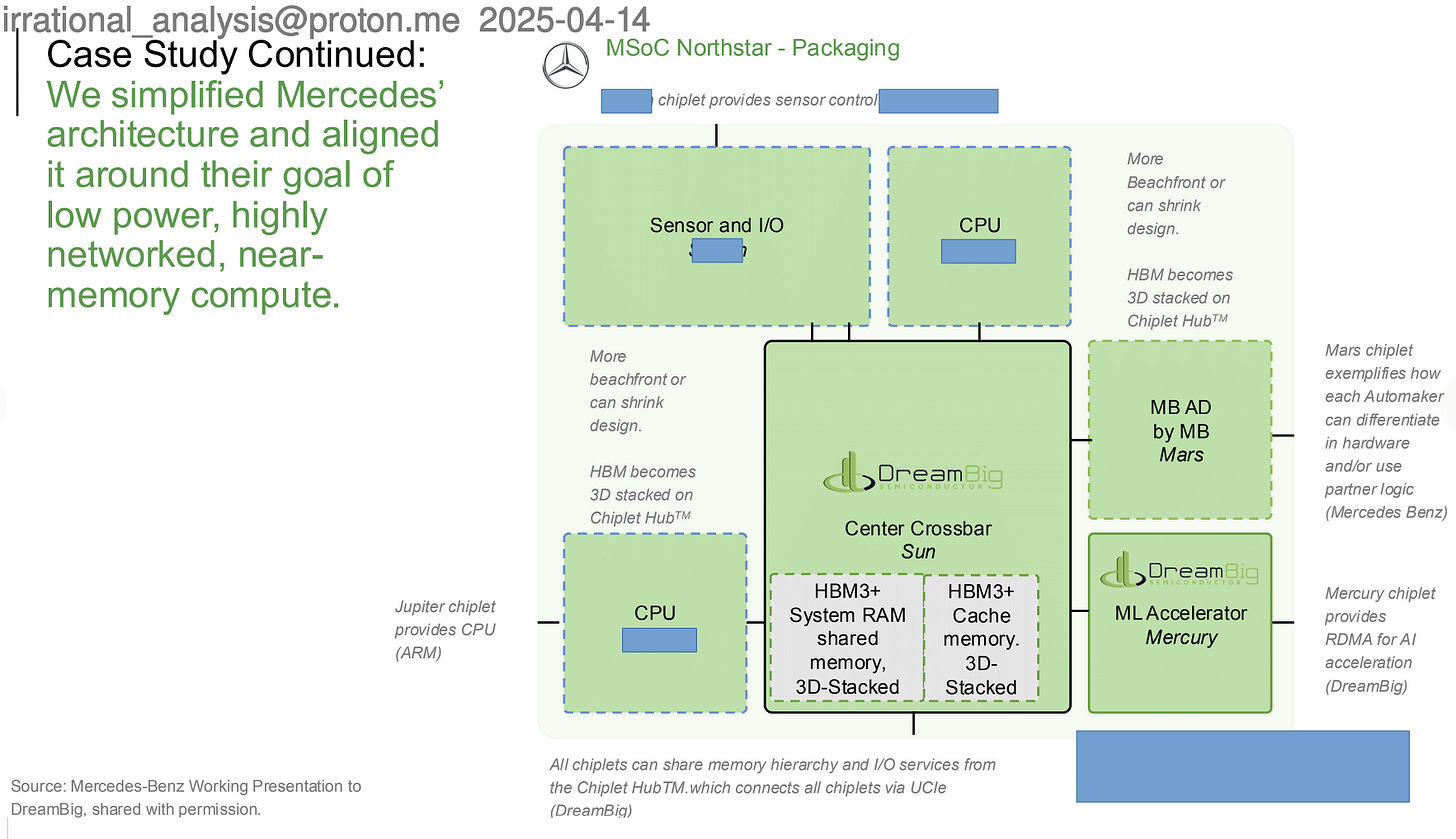

The good news is that DreamBig has a lead customer, Mercedes-Benz.

Obviously, it’s good to have a lead customer generating revenue via NRE.

What is more important is this project will enable DreamBig to learn so much. Debug lots of problems and solidify the platform.

Multiple partner chiplets (using a variety of UCIe PHYs) are involved.

This heterogenous setup (CPU, AI ASIC, sensor) will generate a diverse traffic pattern that will stress DreamBig RDMA and NoC IP.

Packaging will be a critical issue and a real project is critical to learning yields.

Speaking of packaging…

Silicon Box, Packaging, and Key Risks

DreamBig’s 800G NIC will be commercially successful as it is monolithic and hinges on their internal (digital) RDMA IP. Given the pedigree of this team, I am sure the Mercury NIC will work out.

I can’t hold the same confidence for these ambitious projects involving the Demios chiplet hub. Advanced packaging is key, and a lot can go wrong.

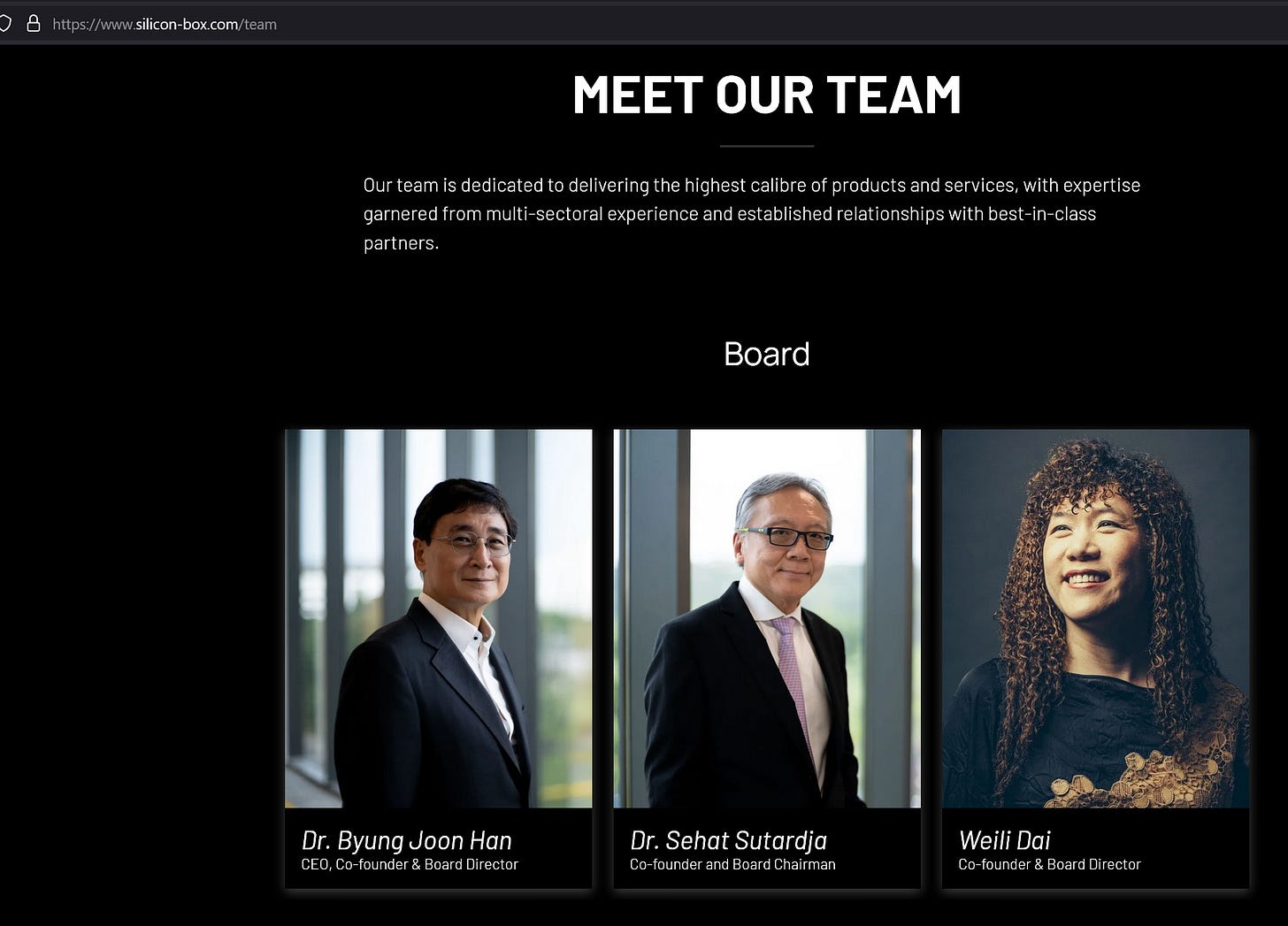

Meet Silicon Box, a related-party startup.

As you can see, these two companies share Weili Dai and Sehat Sutardja (old Marvell power couple) as co-founders.

Silicon Box is an advanced packaging company. Their secret sauce has something to do with panel-level packaging.

A lot of secrecy around how Silicon Box achieves their density and yield claims.

From my perspective, Silicon Box is the biggest risk to DreamBig’s ambitions.

Four Possibilities

DreamBig internal presentations show detailed modeling for target ASP and gross-margins.

The above slide is for their Mercury NIC which consists of two chiplets.

Gross margins are a reflection of the value delivered by a product and DreamBig is (correctly) modeling amazing ASIC Unit Margin.

My concern is that BoM Allocation to ASIC goes down if Silicon Box does not deliver. TSMC will eat into DreamBig overall (product-level) margins.

For the Mercury product, this is fine. Financial outcome will still be great even if this product (two chiplets) needs TSMC CoWoS-S.

The chiplet-hub based products will be hit hard from a gross-margin perspective as TSMC eats more and more of the “rest of BOM” budget.

Even if Silicon Box completely fails (scenario #3), DreamBig works as an investment in my opinion.

There is a risk that some analog-level bug is found in the Demios Chiplet Hub, requiring a re-spin with the UCIe PHY swapped.

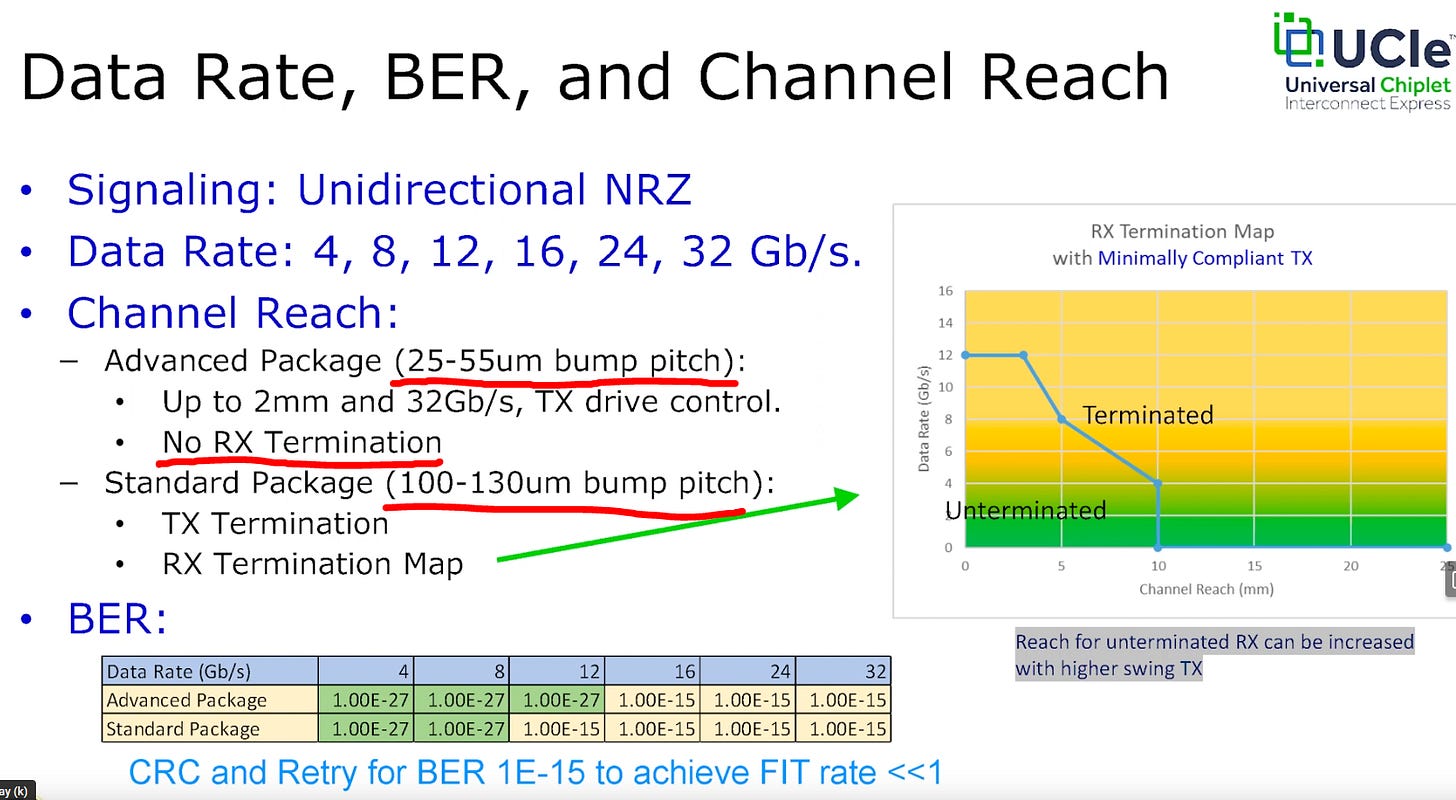

For context, there are actually two versions of UCIe PHY, advanced package and standard package.

Unlike most standards, UCIe explicitly defines PHY bump-out.

There is a very low probability (< 1% in my opinion) risk that some problem with the ambitious Demios chiplet hub necessitates a swap from UCIe-AP to UCIe-SP. This would delay all Demios-dependent products by around 6-months because of a respin.

Packaging Debate with DreamBig:

When I met with Tenstorrent, I spent ~40 minutes pressing them on latency because I was concerned their ability to inference large models would be limited by their mesh NoC and Ethernet latency.

Tenstorrent and the State of AI Hardware Startups

Irrational Analysis is heavily invested in the semiconductor industry.

They showed some internal-only initial benchmarks of Llama 3 in November 2024 alongside latency reduction progression. Given their confidence and transparency, I gave them a pass and wrote a broadly positive post.

Four months later, Tenstorrent held a public developer day and shared the results they previously showed me privately.

https://tenstorrent.com/developer-day

A similar situation happened with DreamBig regarding advanced packaging via Silicon Box. Will the yield be economically viable? Have they thought about insertion loss and crosstalk for so many UCIe-AP and Ethernet PHYs packed together?

Here is a summary of a roughly ~1 hour conversation between myself, Sohail, and the DreamBig investor. I basically confronted these two and tried to get assurances that these ambitious plans are viable given the partial dependence on Silicon Box.

#1 TSMC CoWoS is too expensive.

Sohail said started out with this argument and I agree. DreamBig is unlikely to have enough volume to amortize CoWoS costs as much as they would like.

As an aside, there is currently no viable alternative to TSMC CoWoS. I maintain my virulent distain towards the clowns at Intel Foundry’s advanced packaging department.

Silicon Box is clearly ahead of IFS advanced packaging.

#2 If Silicon Box fails, DreamBig will just use CoWoS.

Given that UCIe defines bump-out, all DreamBig chiplets should be simultaneously compliant with Silicon Box and TSMC design rules.

It will take some work to design a new package. Maybe have two engineers working really hard over six weeks. Not a showstopper from a roadmap perspective. This just hurts DreamBig gross margins.

#3 Dr. Byung Joon “BJ” Han (Silicon Box CEO) is a genius.

Both Sohail and the VC guy spoke very highly of Silicon Box, this guy in particular. Apparently, he is a real galaxy-brain. Obviously, both of them really want to believe Silicon Box (strong related party relationships) is staffed by geniuses. My sense from the conversation is that DreamBig genuinely believes in Silicon Box.

#4 Theoretical Conversation

I may or may not have asked questions about Silicon Box for over 30 minutes.

I hope that regular readers of Irrational Analysis understand that I know a thing or two about packaging, SerDes, crosstalk, and communication systems. Therefore, I probably know the right questions to ask.

If this portion of the conversation happened, I would be inclined to have optimism towards DreamBig’s ambitious roadmap.

DreamBig is worth an hour of your time.

If you are part of a semiconductor company that wants to do cool things with chiplets, you should get in touch with DreamBig.

If you are a private market investor interested in investing in high gross margin semiconductors, DreamBig looks interesting.

Sohail seems like a great CEO, both on technical level and an executive level. His passion for networking and chiplets is admirable.

The investor guy (who introduced me to DreamBig) strikes me as exceptional. He is not just some VC partner who writes a check and phones it in for board meetings. This investor is very active, deeply involved in technical aspects, and meaningfully contributes to strategy, roadmap, and go-to-market. Many of the block diagrams were made by him.

DreamBig is a real company with very interesting, ultra ambitious, utterly unique networking products.

Worth a meeting.

Thanks for this very interesting! FYI pretty sure half of the Marvell power couple sadly passed away last year - you may wish to update. J