IMPORTANT:

Irrational Analysis is heavily invested in the semiconductor industry.

Please check the ‘about’ page for a list of active positions.

Positions will change over time and are regularly updated.

Opinions are authors own and do not represent past, present, and/or future employers.

All content published on this newsletter is based on public information and independent research conducted since 2011.

This newsletter is not financial advice and readers should always do their own research before investing in any security.

Hello wonderful subscribers. Astera Labs is a connectivity company that is trying to go public on the AI wave. Recently, Broadcom made an announcement that I view as nothing less than apocalyptic for Astera Labs.

This is an interesting short opportunity.

Contents:

What does Astera Labs do?

Technical Background

SerDes

PCB Stackup

Signal Integrity

Loss, Reflections, and DFE

Jitter, CDR Bandwidth, and Adaptation

Broadcom’s Killing Blow

There is no moat.

[1] What does Astera Labs do?

They make small “extender” chips which are often referred to as retimers.

These retimers enable new design topologies via extended reach and also lower costs by enabling cheaper PCB materials.

Astera Labs S-1 filing and public marketing really loves to highlight their COSMS software management system. “Software-Defined” gets thrown in over and over again to dupe dumb investors. This is not a SaaS business. There is no competitive moat.

[2] Technical Background

To understand the antihalation Broadcom has wrought upon Astera Labs, you must first understand some technical terms.

[2.a] SerDes

SerDes is shorthand for “serializer-deserializer”. USB, HDMI, Ethernet and PCIe are all examples of SerDes. Each protocol has it’s own electrical specification alongside upper-layer operations. For example, CXL has the exact same electrical specification as PCIe. This means CXL is really just an upper layer protocol built on top of the PCIe physical layer.

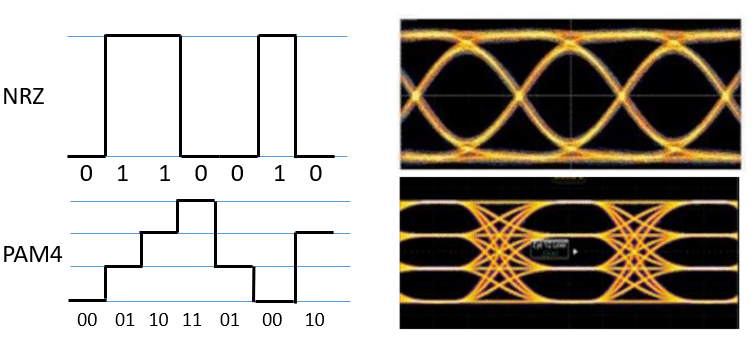

Currently, there are two main types of SerDes, NRZ and PAM4.

NRZ sends one bit per symbol.

PAM4 sends two bits. 00, 01, 10, or 11, depending on the voltage.

PCIe 5 and older uses NRZ while PCIe 6 uses PAM4.

Ethernet made the jump from NRZ to PAM4 around the 100GbE module to 400GbE module generation.

There was some talk that 224G electrical (for 1.6TbE modal) Ethernet SerDes would need to use PAM6 but the standards body (IEEE) decided to stay on PAM4.

A tradeoff exists between modulation order and system bandwidth.

[2.b] PCB Stackup

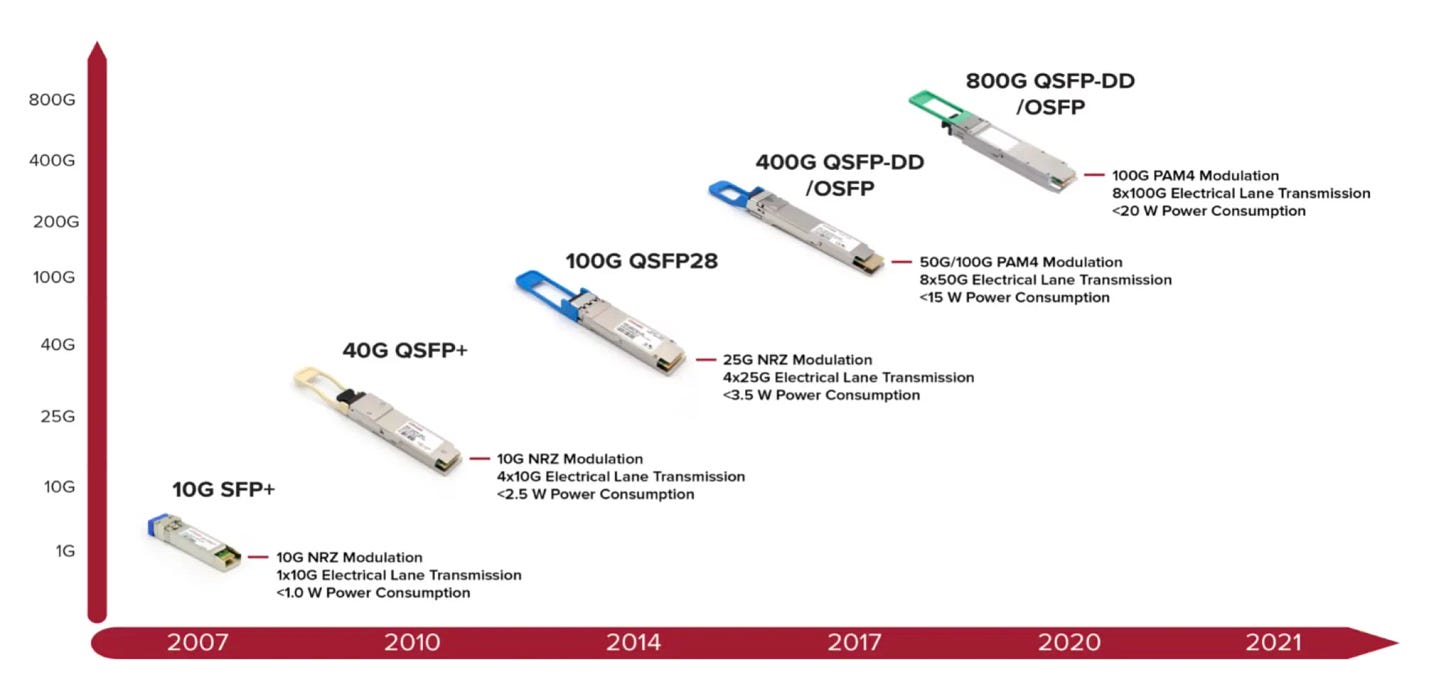

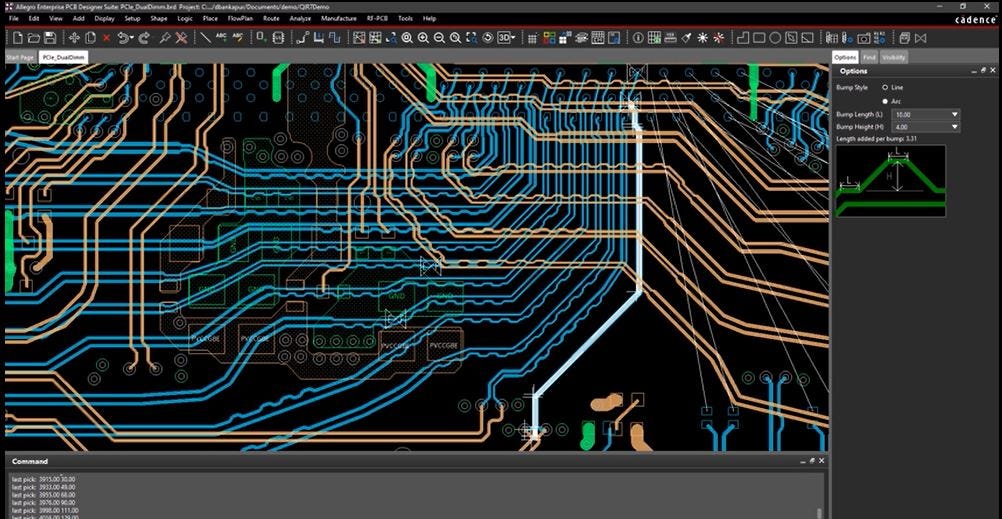

Printed circuit boards (PCBs) are manufactured much like semiconductors except there is no metal deposition. Each “core” consists of a dielectric sandwiched between two solid copper layers. Photomask, lithography, and etch are all applied. Then a “prepreg” layer is added on top before continuing.

The Prepreg can be the same material as the core dielectric or something thicker/thinner/cheaper. Depends on the design.

It is standard industry practice to have all high-speed SerDes (PCIe, Ethernet) on the same layer of a PCB. Expensive materials used on that layer only.

Modern high-end PCBs can have 12-20 metal layers.

[2.c] Signal Integrity

Signal integrity is a very important aspect of board design. Often, there are dedicated engineers who only handle signal integrity, nothing else. Differential traces need precise impedance matching. Load capacitance and impedance of devices need to be modeled. Traces can easily interfere with one another, ruining a design if simulations are not checked properly.

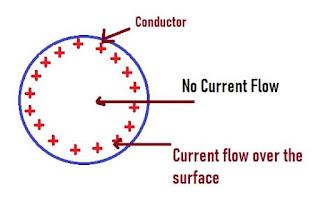

Additionally, the skin effect makes everything much more difficult for high-speed (PCIe, Ethernet) signals. Most of the energy ends up going on the surface of each trace. This means most of the copper metal is not accomplishing much other than providing structural rigidity.

[2.d] Loss, Reflections, CTLE, and DFE

Marketing materials for SerDes often quote loss tolerance. A lot more goes into the quality of a SerDes than just loss.

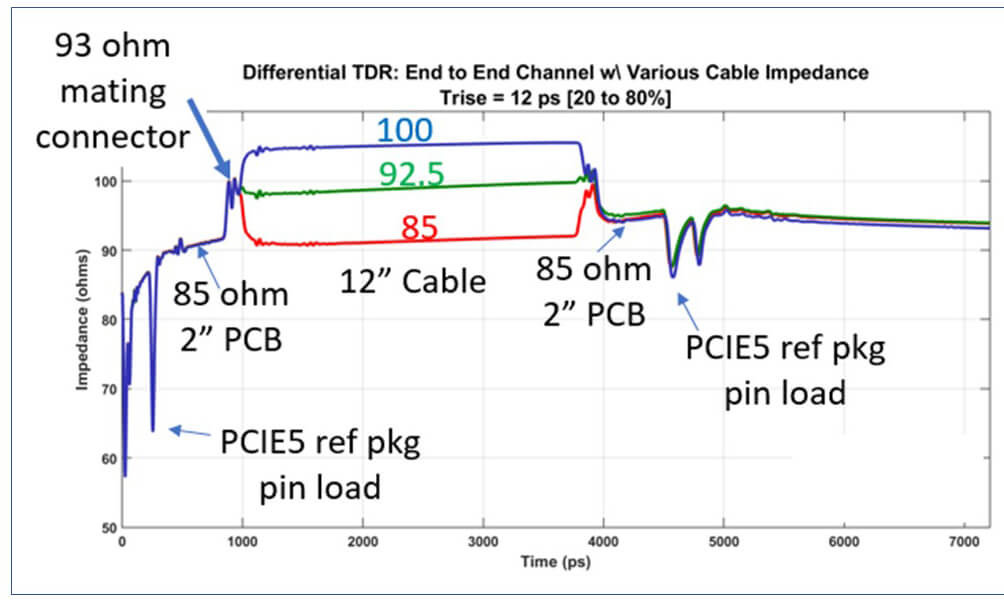

Each type of material induces some amount of loss, measured in (dB). PCB, cables, connectors, and so on.

Insertion loss is really a measurement across frequency. The numbers that get quoted are loss at Nyquist. Faster SerDes use more bandwidth and thus have a higher Nyquist frequency.

The smoothness of a channel is important. Bad materials/cables/connectors can cause unnecessary reflections.

Every time an electrical signal moves to a new medium, some of the energy is reflected backwards. Reflections cause problems for the receiver which must be corrected by some form of equalization/filtering.

Because PCIe spec cares a lot about latency, they do not use digital filtering aka post-ADC FFE. Ethernet places a strong emphasis on digital FIR filtering.

CTLEs are analog circuits that adjust the gain and shape of the incoming signal. Very powerful but very painful to tune, calibrate, and maintain in mission mode.

For example, suppose a link is established when the silicon is at 60C. As the chip warms up to say 110C, the CTLE response changes dramatically, requiring live tuning by firmware.

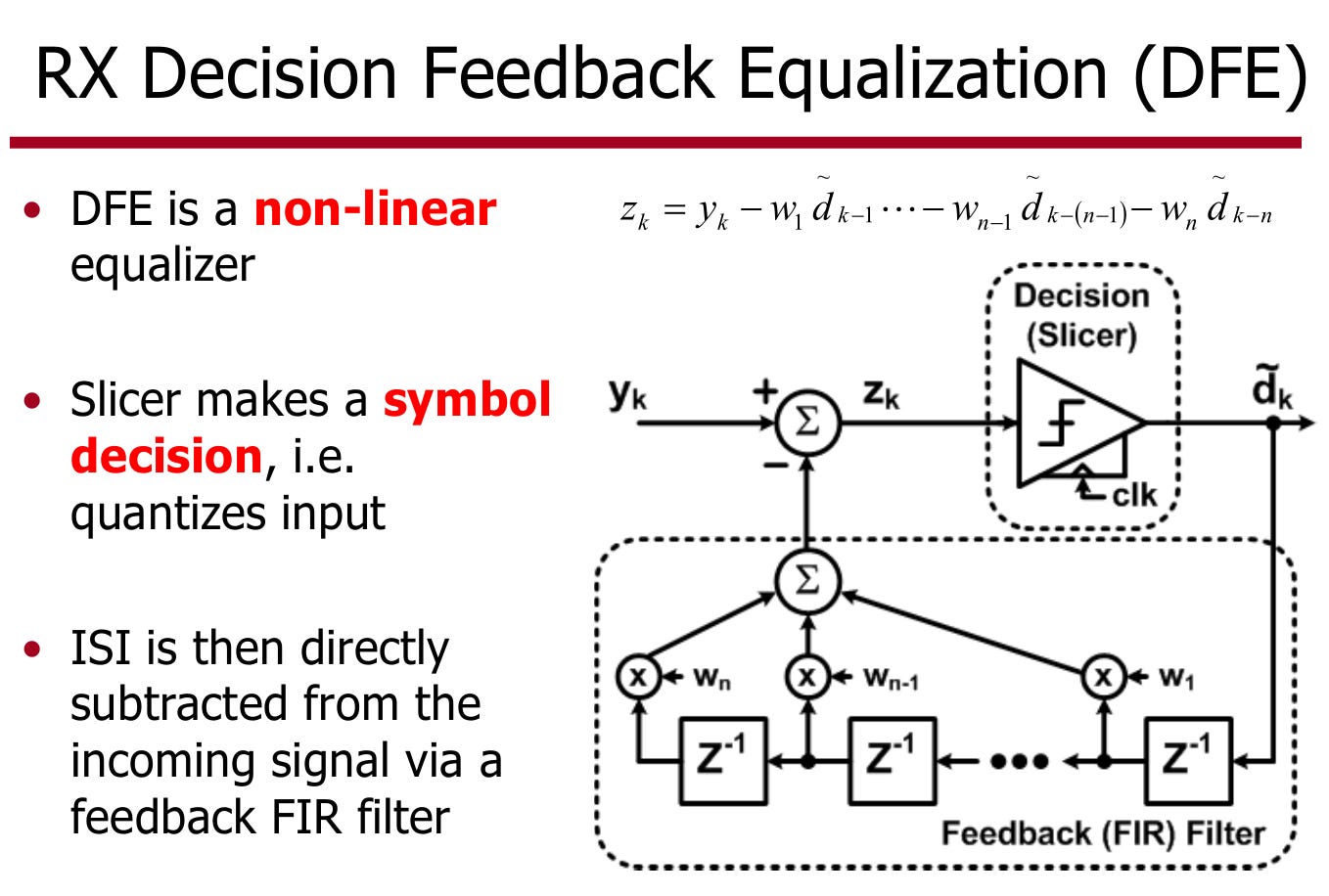

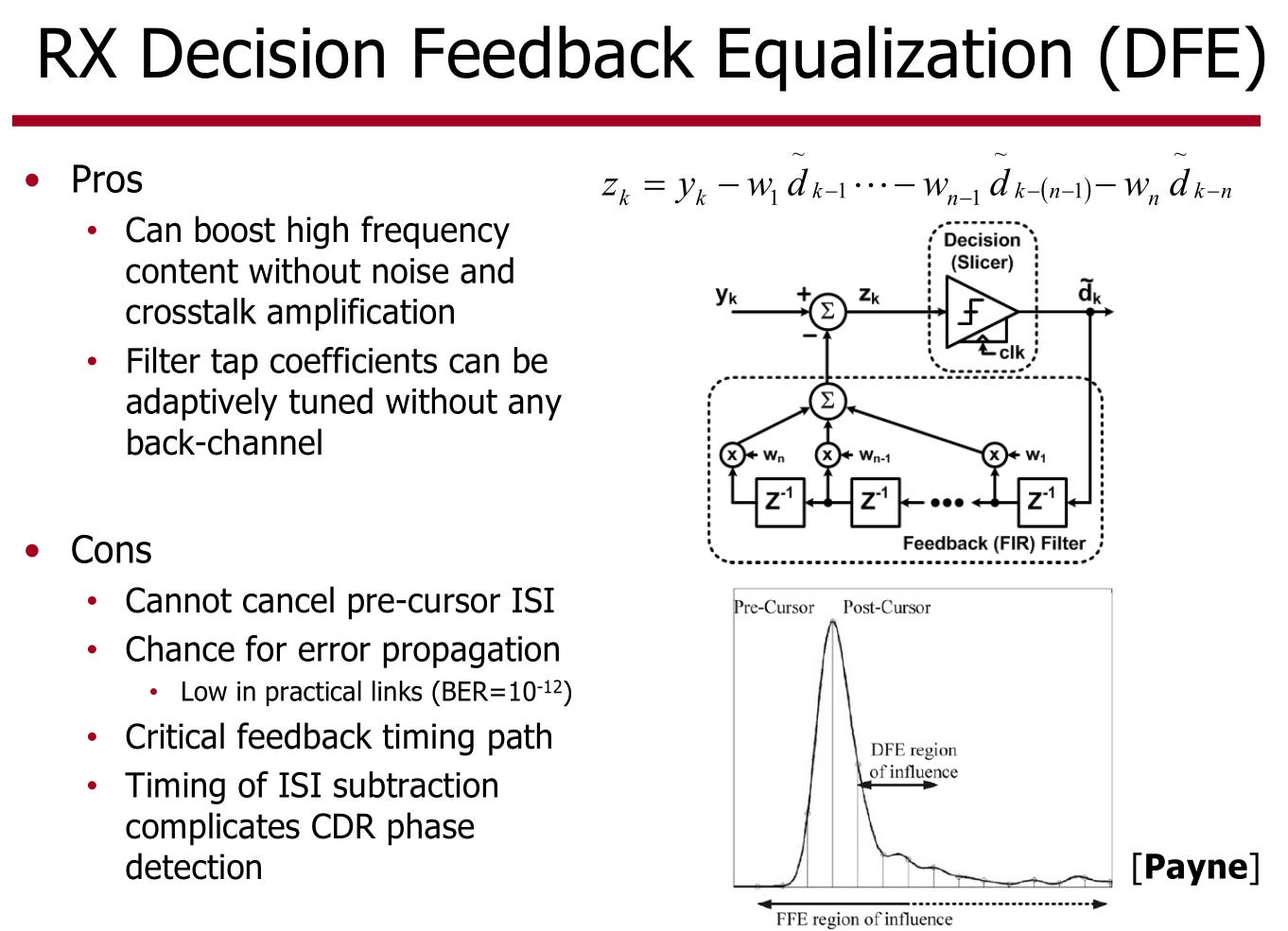

DFE’s are a type of non-linear analog filter. Not quite like a digital IIR filter because of the conditional blocks.

Often, SerDes include extra DFE coefficients for resilience. A higher-quality SerDes (such as Broadcom’s) can turn off some of the DFE coefficients because there is less junk for the receiver to clean up. This saves a lot of power.

[2.e] Jitter, Adaptation, and CDR Bandwidth

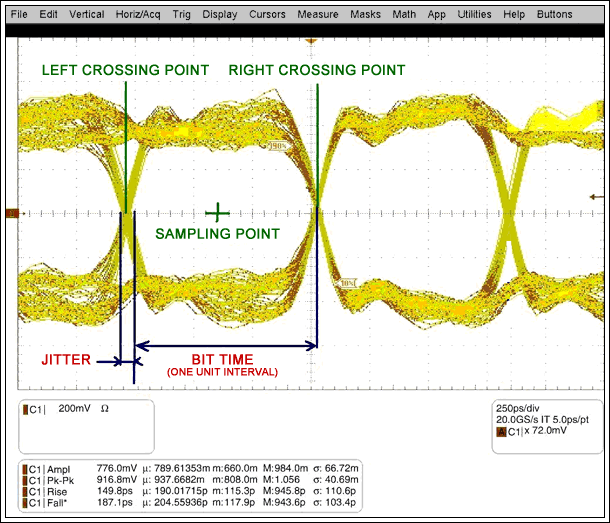

Jitter is an industry term for time-domain noise. There are many types and sources of jitter but I want to keep this simple.

The problem with jitter is when it changes after the link is already up. Suppose you have a PCIe link between a CPU and a GPU. All is well until a neighboring PCIe storage device is hot-plugged in and starts dumping sinusoidal noise into neighboring lanes.

SerDes include various adjustable circuits to alter the jitter rejection profile of a particular lane. How the firmware handles these situations in mission mode is very important. CDR design and tuning is a subject on it’s own.

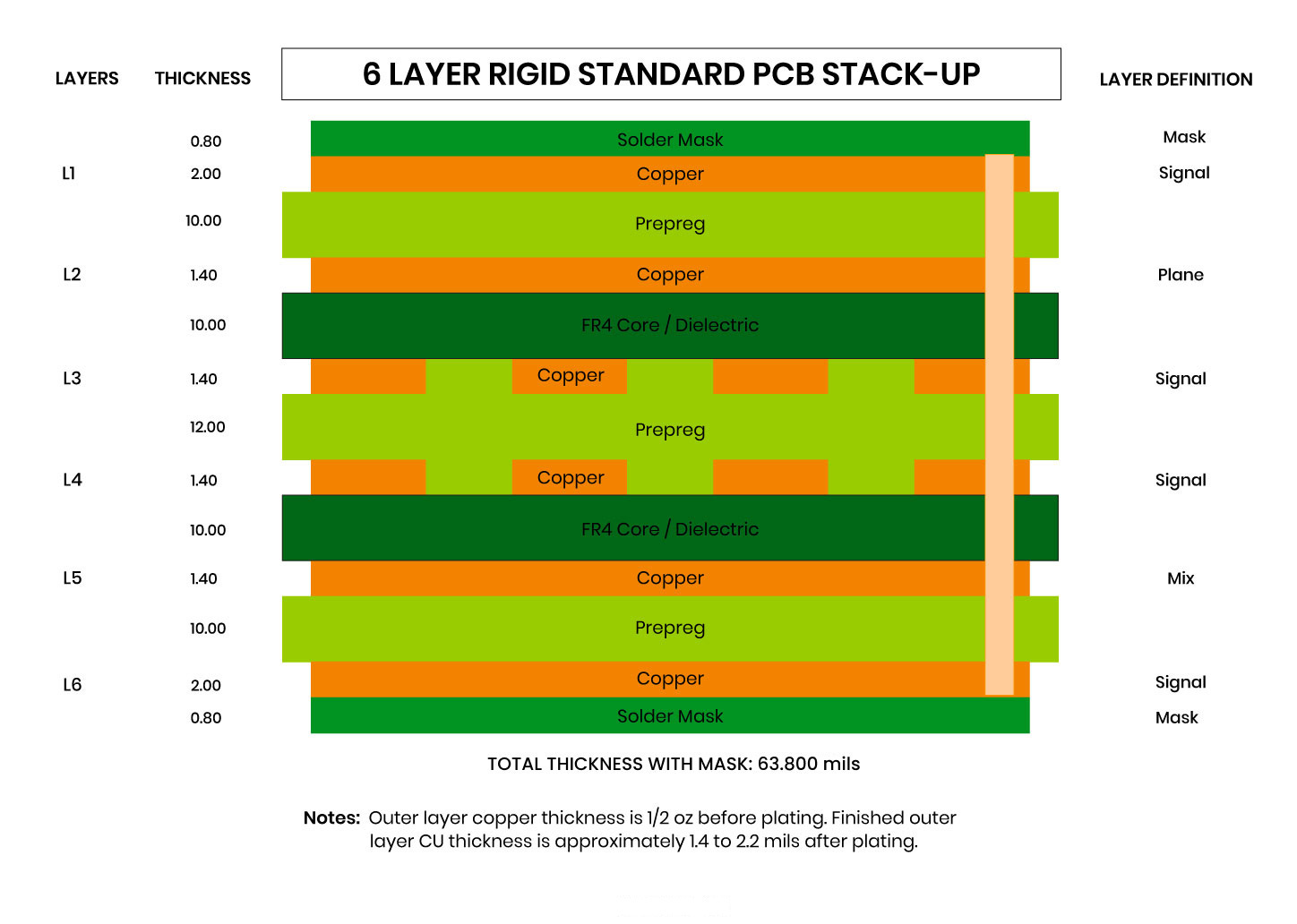

[3] Broadcom’s Killing Blow

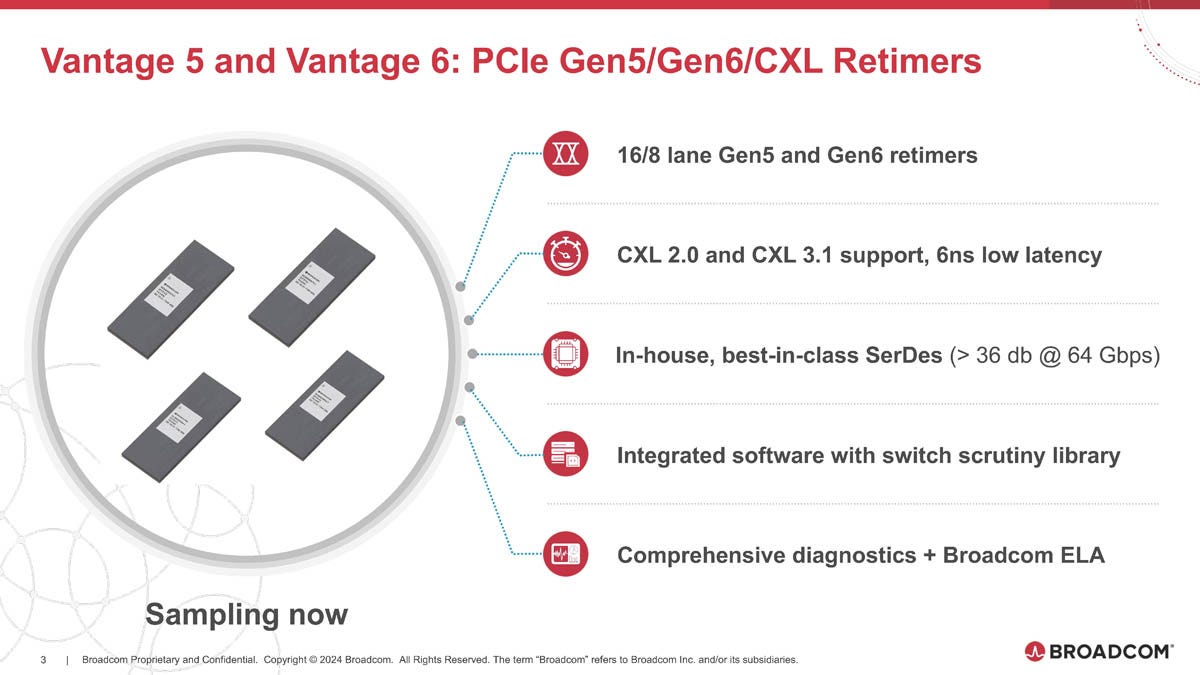

Amusingly, Broadcom decided to make some major product announcements right as Astera Labs is trying to IPO.

I have made some minor modifications to the official Broadcom marketing slide. It is not fair for them to state Astera’s solution is > 32 dB because most references to loss within datasheets is > 36 dB. Seems like a cherry-pick.

Regardless, they should be terrified.

Broadcom has:

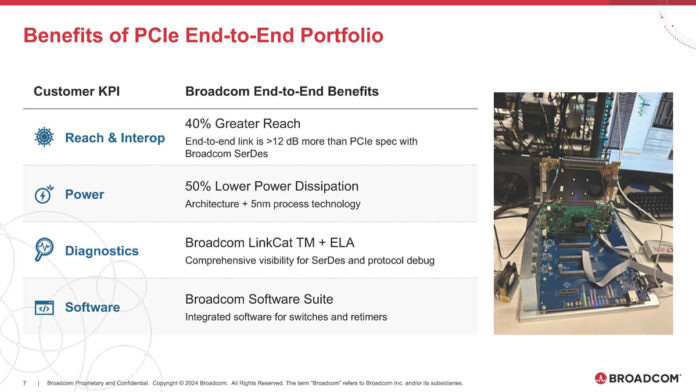

2/3 the power draw at Gen5 and stills wins on Gen6/PAM4 power!

This is plausible because of full process node advantage.

Also better SerDes quality enabling fewer DFE taps.

Drop-in PCIe Gen6 compatibility.

4-9 dB of guarantied extra reach. MASSIVE!

Better software ecosystem.

Industry-leading interoperability.

[4] There is no moat.

Astera Labs loves to hype up their COSMOS software as a major differentiator and moat. It is not either of those things.

Having an upper layer software stack to collect telemetry on CTLE settings, CDR bandwidth, DFE configuration, temperature, … and so on is normal. Broadcom’s diagnostic stack does all these things and more.

Broadcom is the leader in PCIe network switches and NICs. Their monitoring software is industry leading.

Astera is way behind on power.

Has no PCIe 6 product.

Is way behind on link budget (loss) margin.

Is way behind on interoperability.

There is no competitive moat for Astera Labs because Broadcom has all the moats.

Astera Labs has until late summer 2024 to put out a new product and try to compete in the low-end. Otherwise, everyone is going to design them out, switch to Broadcom’s retimers, and save a huge amount of money on CapEx (cheaper PCB designs, cheaper cables, cheaper connectors) and OpEx (power burn, stability/downtime),