Marvell and Intel Catch-Up Note

Two dumpster fires shine bright.

Irrational Analysis is heavily invested in the semiconductor industry.

Please check the ‘about’ page for a list of active positions.

Positions will change over time and are regularly updated.

Opinions are authors own and do not represent past, present, and/or future employers.

All content published on this newsletter is based on public information and independent research conducted since 2011.

This newsletter is not financial advice, and readers should always do their own research before investing in any security.

Feel free to contact me via email at: irrational_analysis@proton.me

I am still on break but news too interesting. Gotta push this shitpost out.

(break is going great btw. very relaxing)

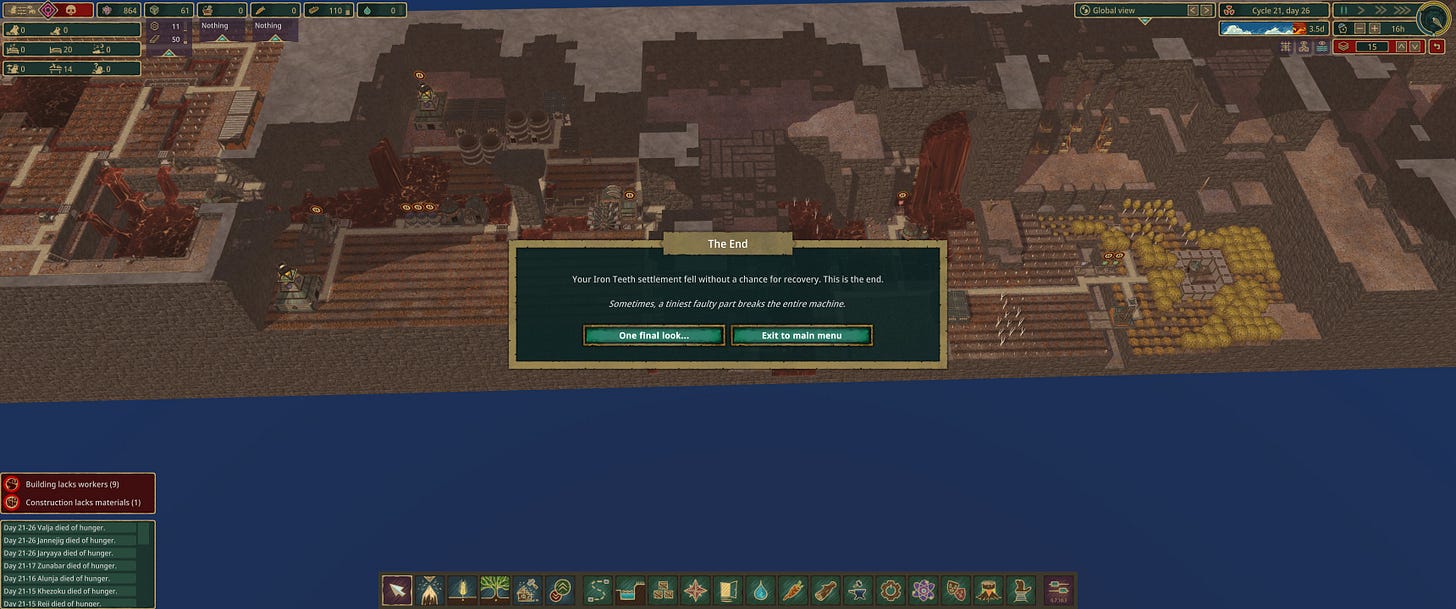

Time limit for this post is 1 hour. My current beaver colony almost died and I am waiting for the population to slowly re-build.

Marvell:

Apparently, I am very infamous amongst Marvell executives. Admittedly, the last post was a little excessive but turns out, I was right.

“ The Trn2 Max program is at leas on hold because of challenges in [Marvell] SerDes performance. The Trn2 Max program was expected to deploy four ASICs per compute tray.

Trn3 appears to be experiacing setbacks. We hear that original designer Alchip has run into SerDes performance issues and hat to re-spin. That drove AWS to engage with MRVL as well but their SerDes performance isn’t without challenges either. It appears both suppliers had to do a second tape out recently, implying Trn3 MP in 2H26.

— Edgewater Securities Research Note (6/18/2025)

“Microsoft is evaluating which silicon partner to team up with, having been disappointed with Marvell’s networking performance.”

— Semianalysis Accelerator Model Note (6/24/2025)

Marvell executives, do you jokers have nothing better to do than go after hobby shitposters? Why don’t you spend time fixing your fucking SerDes?

Do you want to get me fired from my dayjob? Be careful what you wish for. Imagine the damage I can cause as a full-time corporate terrorist. Unlike sell-side, I do not give a shit about “access” to corpo scum.

To be clear, my last post was about how the optical-side 200G SerDes was bad. The Edgewater and Semianalysis notes talk about how the KR (long-reach electrical) 200G SerDes and PCIe 5/6 SerDes suck.

Let’s go over the Marvell Custom AI Investor Event 2025 slides.

XPU attach is massive cope that is trying to distract investors from the disasters that are Amazon/Trainum and Microsoft/Maia.

Google is (allegedly) moving their next generation ARM-based CPU project to GUC.

Amazon is most likely moving Trainum 4 to Alchip + Astera Labs (IO die with a shit ton of re-timers).

Microsoft is also looking to leave and has fucked up so bad that near-term volume is gona be super low. It looks like they tried add features to the digital logic and botched timing closure. Killed performance and TCO. Ima throw u a bone Matt Murphy. The Maia 200 Braga epic fail is probably 10% your [Marvell’s] fault and 90% Microsoft’s fault.

*Also, the rumors that 20% of Microsoft Maia team has left is hilarious. When engineers leave en-mass, it is usually because management went full-retard.

Also, Matt Murphy aggressively tried to hint that XAI is one of the “emerging hyperscale” custom XPU sockets. He is trying to hype up that [WRONG] call from the Citigroup clowns. Multiple sources have told me that XAI is NOT with Marvell for custom XPU.

AWS is so happy with Marvell that they couldn’t be bothered to have a suit recite the bullshit quote in a pre-recorded video.

Congratulations Marvell, you just made the investment case for Broadcom. “Full-service” margin profile only works if you deliver real value. If Alchip and Astera Labs can splice together Synopsys/Cadence SerDes IP for way cheaper, you [Marvell] have no reason to exist.

I actually laughed out loud when I saw this slide while watching the livestream.

Yes, Marvell does publish lots of papers at ISSCC.

These are nice papers. Please keep publishing.

So if publishing IEEE papers is such a key metric, why has Broadcom (rarely publishes) repeatedly whooped your ass?

I saw this 3nm 224G SerDes 50dB bump-bump demo in person at OFC. It was not good. Came back twice to check that it really was that mediocre.

4e-8 pre-FEC BER with plenty of errors at FEC symbol 9.

This was with aggressive active cooling (super high airflow fans) on the chip.

Marvell keeps trying to show sell-side analysts sneaky demos.

Here is a guide on how to spot cheesed demos:

Ask what the die temp is. Anything under 90C is too optimistic.

Ask if the channel has RSS_DFE4 greater than 0.05

If they show you an eye on a scope, make sure the oscilloscope is displaying “D1A”. All modern Keysight scopes have touch screens. Just tap the top right corner to check for sneaky behavior.

Do not accept pre-FEC (raw) BER as a performance metric. Ask to see the entire Reed-Solomon FEC table. Any errors after FEC symbol #8 is bad. Broadcom regularly delivers performance such that FEC symbol 4/5 have no errors.

Ask them to bring the “TT” tray to you. Replace the two chips in the demo with random TT parts from the tray of your choosing. It takes less than a minute to do this. Do not let them bullshit you that this request is “too time consuming”.

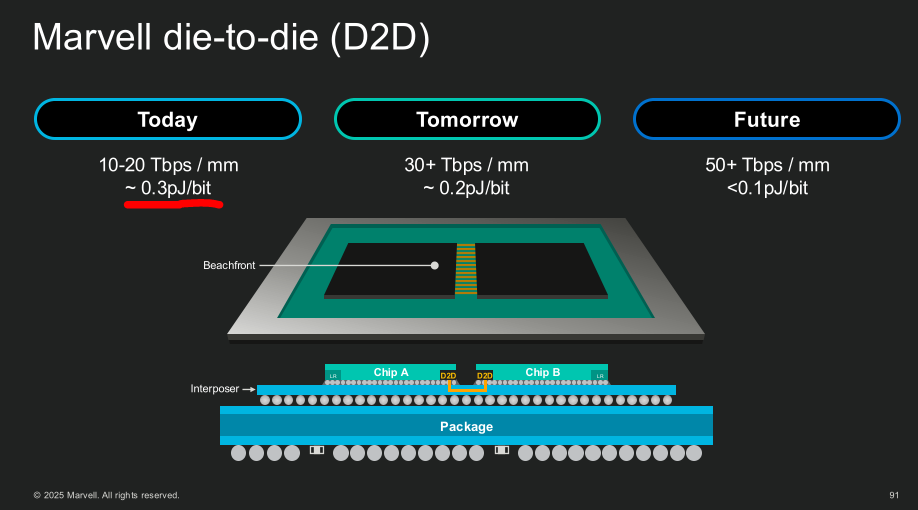

0.3 pJ/bit is basically tied with off-the-shelf D2D IP from Synopsys and Cadence. Broadcom MAX is better.

This super dense SRAM is actually cool. Good job. Credit where credit is due.

Everyone is customizing HBM4 base die. Moving controller and parts of the PHY to the base die is a common strategy.

This power delivery tech is also pretty neat. Wish there were more details. Honestly this PIVR tech deserved more slides and detailed coverage.

I see lots of fibers. Looks like MZI modulators with who knows how many discrete external lasers. Not many details which is unfortunate.

Intel:

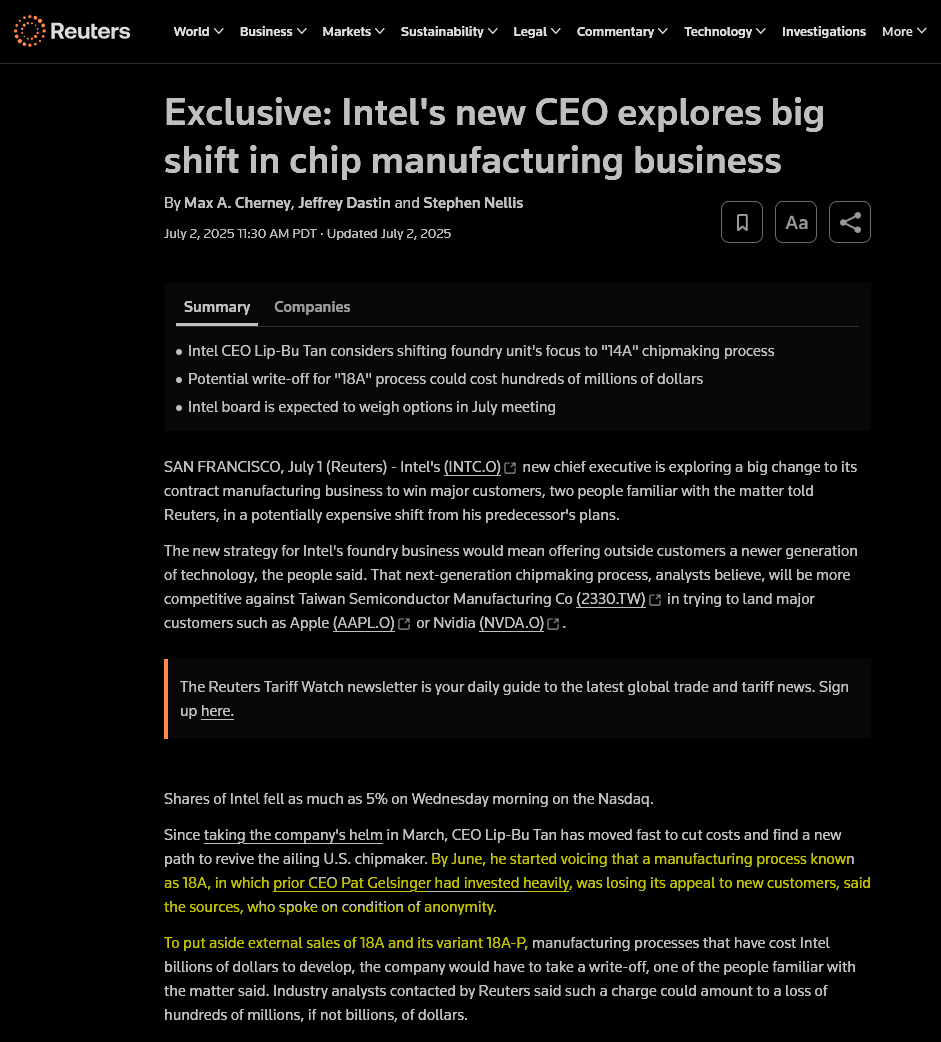

Both 18A and 18AP appear to be toast. I love how despite increasingly insurmountable evidence that I WAS FUCKING RIGHT FOR OVER A YEAR, Intel fans still find a way to move the goalposts.

It looks like 18AP is too late. TSMC N2 is too far ahead and Intel Foundry missed its time-to-market window. 18A/AP competes with TSMC N3P you dipshits. Get that back-side copium outta here. If you have to blow up area to add margin for super high process variation, why the fuck does it matter that IFS is first to backside power?

Also, Lip-Bu Tan is privately telling buy-side analysts that parametric yield of 18A is terrible.

Well we are at the end of my 1 hour timer.

All of my beavers died, just like the hopes and dreams of Marvell and Intel Foundry.

Time to re-start the map.

https://mod.io/g/timberborn/m/quest-for-the-ancient-aquifer-2#description

Need to prioritize badtide diversion system.

Welcome back! We ve missed you 😆

The Beavers! 23 hours to the beavers, and one hour to the stock talk = much happier soul.