Irrational Analysis is heavily invested in the semiconductor industry.

Please check the ‘about’ page for a list of active positions.

Positions will change over time and are regularly updated.

Opinions are authors own and do not represent past, present, and/or future employers.

All content published on this newsletter is based on public information and independent research conducted since 2011.

This newsletter is not financial advice, and readers should always do their own research before investing in any security.

Feel free to contact me via email at: irrational_analysis@proton.me

I am writing this very quickly before heading over to downtown SJ for meetings and parties.

(quality is low… sorry lol)

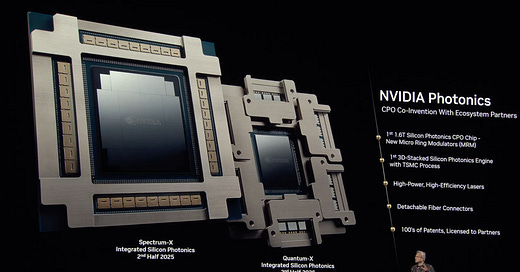

Let’s talk about TSMC COUPE.

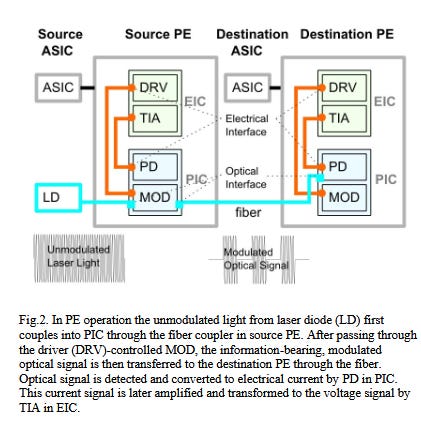

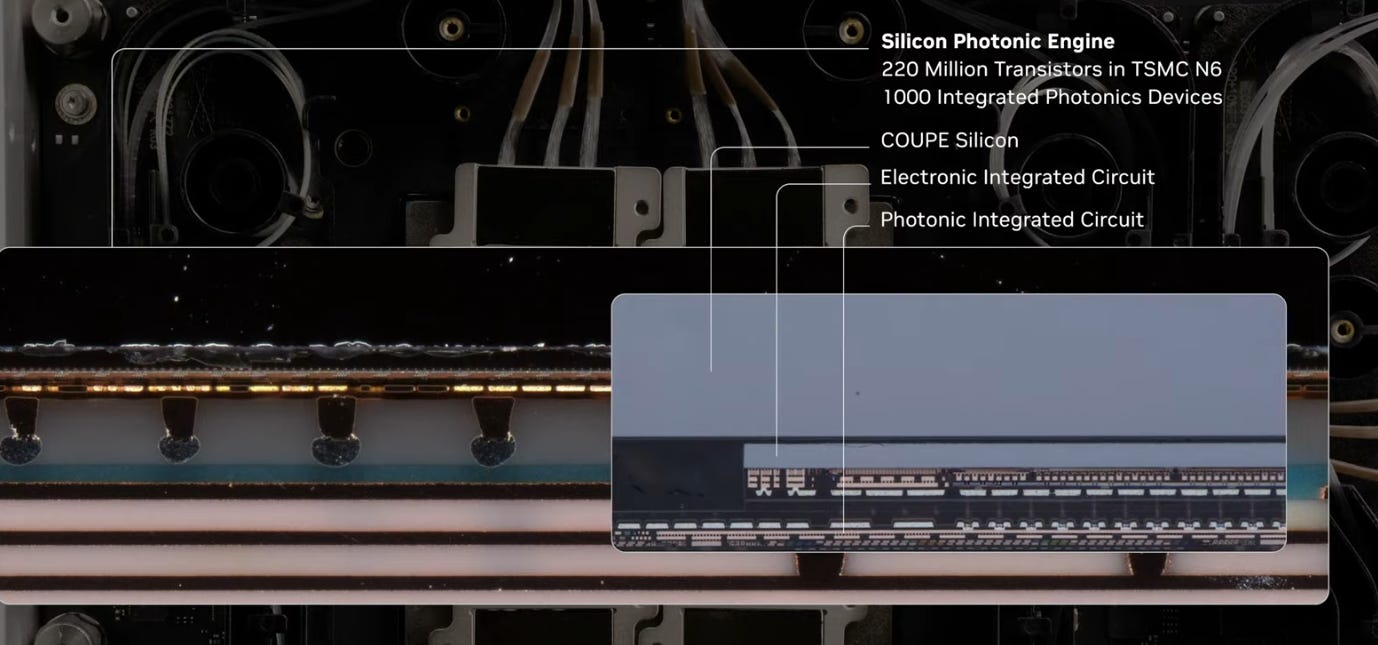

Optical things (resonators, phase detectors, photodiodes, modulators, waveguides…) need to be on a special process node. A photonic process node.

The chip with all the optics bits is called photonics IC or PIC.

But the PIC is very Finkey. There needs to be an electrical signal that is at just the right voltage for this to work.

Thus, we have the electrical IC, aka EIC.

This chip is built on a normal logic node and has one job. Make sure the electrical signal going in/out of the PIC is just right.

Why not directly drive the PIC from the ASIC you might be thinking?

Even with (most) advanced packaging, the electrical signal coming out of the ASIC gets too fucked up to directly drive. (this is consensus opinion not my opinion)

The true silver bullet is directly hybrid bonding the PIC to the ASIC.

Hybrid bonding PIC to ASIC brings many challenges such as impedance mis-match, reliability, cost, and so on…

Many elements on the PIC are controlled by thermals. Tiny heaters.

The caveman way of integrating an EIC and PIC is to use some form of vanilla packaging (RDL).

COUPE is different.

TSMC hybrid bonds the EIC and PIC.

This is really fucking good.

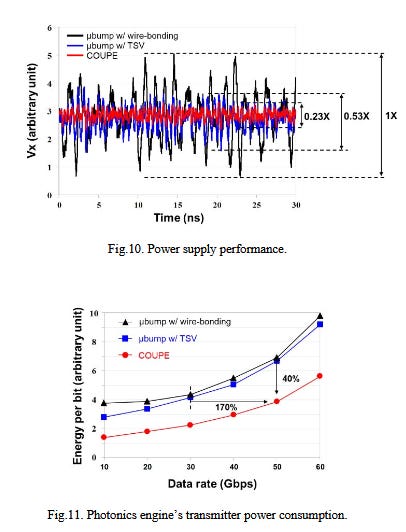

Parasitic capacitance very bad. It causes so many problems for the package designer and SerDes design.

COUPE has 85% less parasitic capacitance.

Insertion loss is basically zero. The 0.2 dB gain is not that big of a deal though.

20 dB of extra return loss is MASSIVE.

Here is an analogy I keep using with the finance friends. It seems to work.

Imagine you are a singer.

You have a big audience.

One way of making sure everyone hears you is to sing louder.

But at some point, your voice will become distorted and certain frequency tones (high notes… baratone… whatever) become distorted. The quality of your voice becomes shit.

In general, this is a fixable problem. With proper training, you can make the muscles in your vocal cords stronger, allowing you to sing louder at the same musical quality.

But what if the venue has echos?

That is a much more difficult problem to solve…. right?

insertion loss == how weak signal become

return/reflection loss == how much signal echo

Communication systems need DSP/retiming mostly to deal with reflections.

The peak of package impedance is moved to higher frequencies. This is very nice.

Circuits are intrinsically sensitive to power supply noise. This is called PSRR.

COUPE makes the noise much lower which is great.

Sidenote: I would not take the energy efficiency plot from this TSMC paper too seriously. There are many variables at play here and the baseline they have is not realistic. It’s better but there are way too many factors to just take that 40% number at face value.

In summary (wana hammer this home):

COUPE insertion loss nice but whatever.

COUPE return loss fucking mazing.

Supply noise performance very nice. Adds margin to system.

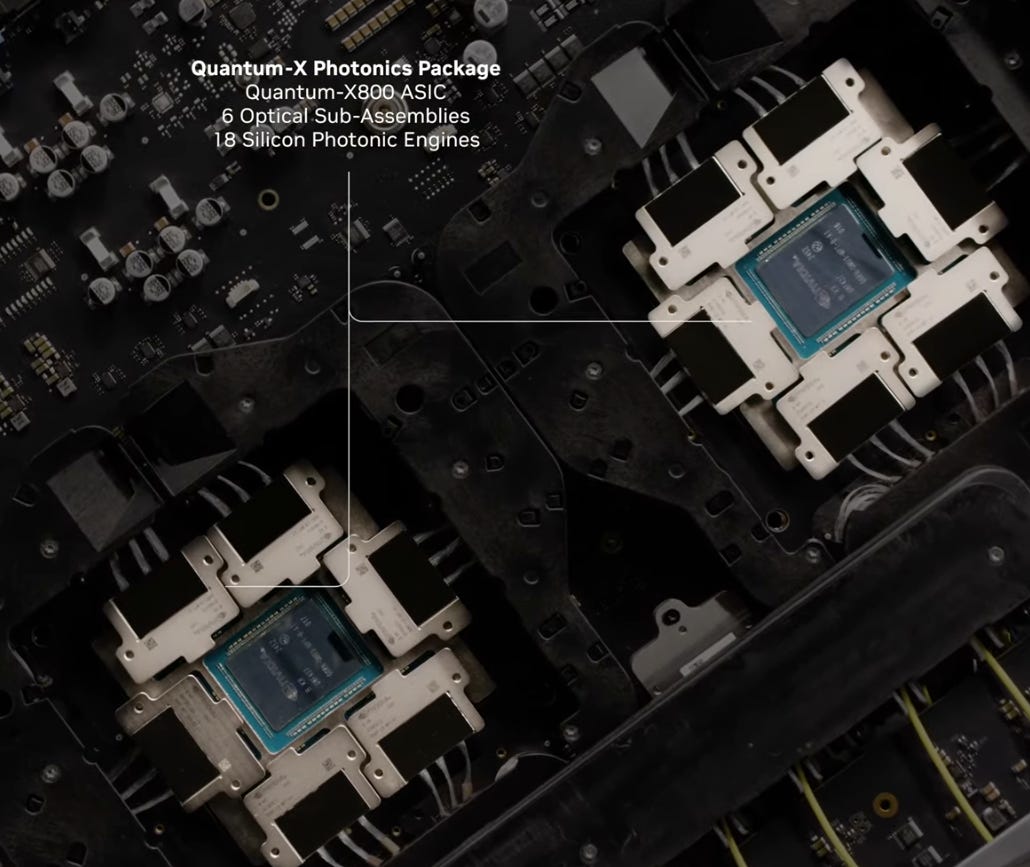

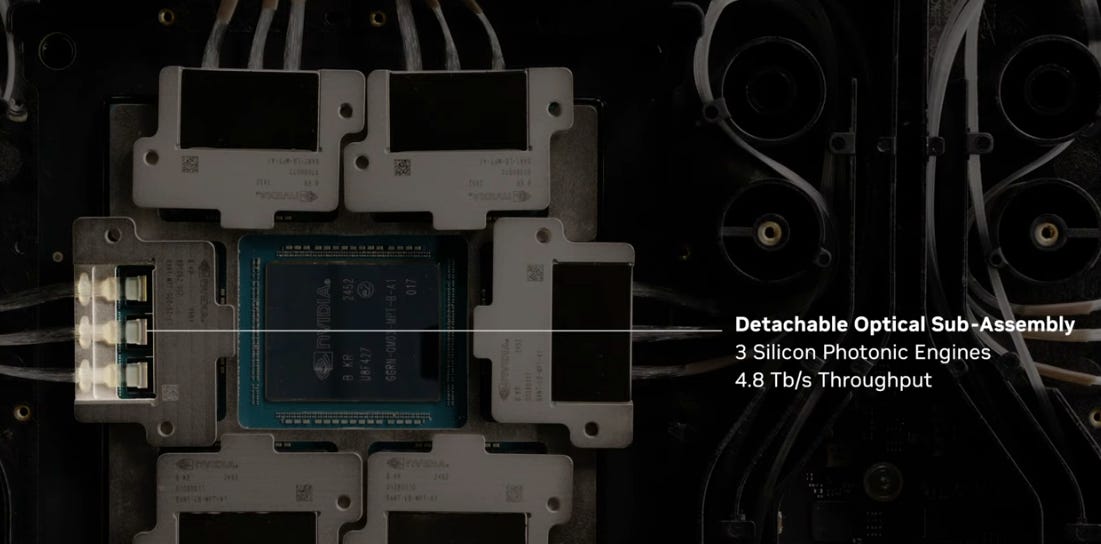

It took three levels of zoom to get to the important bit.

They are using micro-ring modulations.

For now, all you need to know is these micro-ring things are EXTREAMLY SENSITIVE to temperature.

They are literally controlled by temperature.

This is why silicon photonic engine cannot be hybrid bonded directly on top of the switch chip.

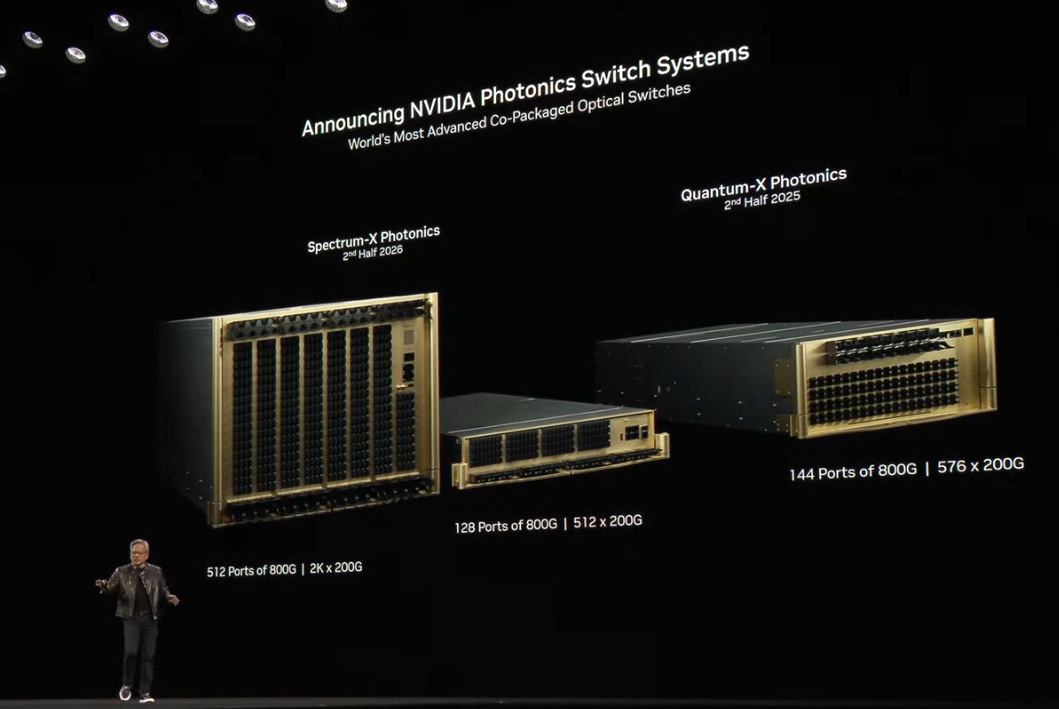

I have been doing a lot of research into CPO because…. reasons.

Can you guess why I have been so busy recently?

If someone could get Lightmatter to talk to me that would be great. Wana complete due-diligence.

Will write a detailed primer on CPO once I have time. There is a placeholder on my calendar but again… very busy. Both dayjob busy and other efforts.

COUPE is where the hybrid bonding happens and this is why CPO in this form is possible.

And now you know why the switch chip cannot directly drive PIC. It is too far away. EIC is needed to re-shape and amplify the signal.

You can build TIA (basic class of amplifier) and more advanced multi-stage, highly configurable/tunable CTLE on the EIC.

Lots of options. Again, details in the upcoming (at some point lol) CPO mega-post.

The laser sources are pluggable. This is because they are super unreliable.

Primary point of failure. Serviceability of the light/laser source is a must.

Would you mind elaborating the impact on Arista? Thx!

CPO will be mainstream in the future.